|

市場調查報告書

商品編碼

1910505

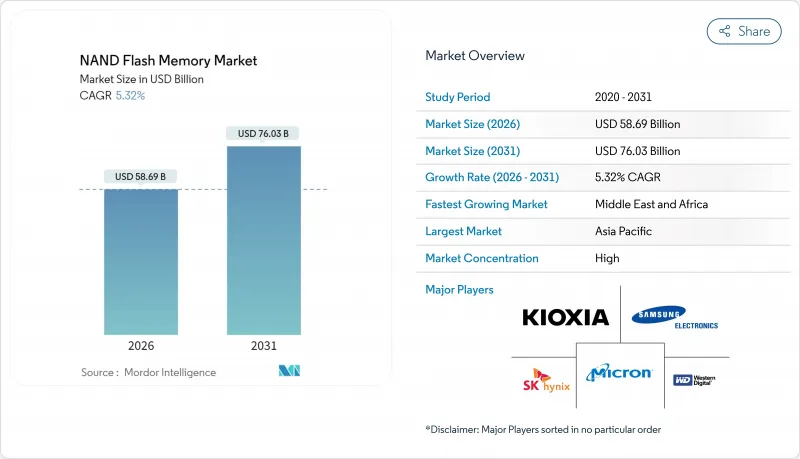

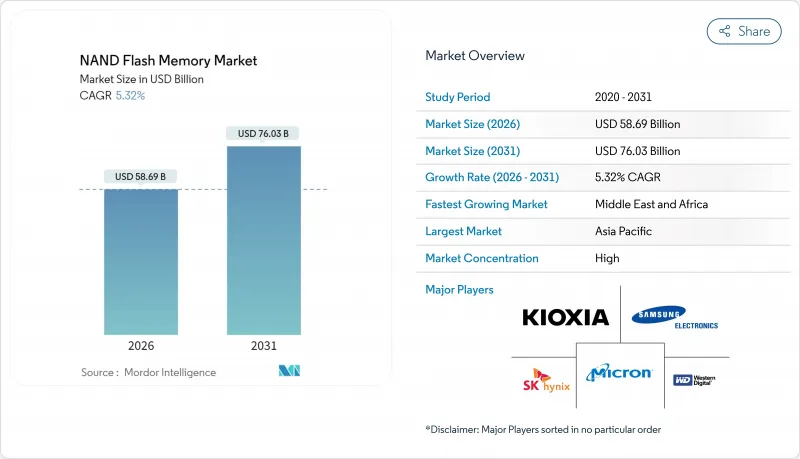

NAND快閃記憶體:市場佔有率分析、產業趨勢與統計資料、成長預測(2026-2031年)NAND Flash Memory - Market Share Analysis, Industry Trends & Statistics, Growth Forecasts (2026 - 2031) |

||||||

※ 本網頁內容可能與最新版本有所差異。詳細情況請與我們聯繫。

據估計,2026年NAND快閃記憶體體市場規模將達到586.9億美元,高於2025年的557.3億美元。預計到2031年,該市場規模將達到760.3億美元,2026年至2031年的複合年成長率為5.32%。

這項穩定成長的驅動力來自超大規模資料中心在人工智慧訓練叢集的資本投入、客戶端PC和遊戲主機向固態儲存的轉變,以及垂直堆疊式3D架構帶來的每位元成本持續下降的趨勢。同時,各國為促進半導體製造在地化而推出的獎勵,尤其是在美國和沙烏地阿拉伯,正在增強區域供應鏈的韌性。突破300層以上的技術進步以及PCIe 5.0的普及,正在縮短企業級和消費級固態硬碟的更換週期。 5G部署和大量物聯網終端的整合進一步擴大了潛在需求,使NAND快閃記憶體體市場有望保持持續的個位數溫和成長。

全球NAND快閃記憶體體市場趨勢與洞察

資料中心對人工智慧/機器學習儲存的需求快速成長

超大規模營運商正在重新設計儲存層級,將NVMe SSD池部署在靠近GPU叢集的位置,從而為搜尋密集型生成工作負載提供每秒數GB的吞吐量。西部資料預測,到2029年,僅5G終端的NAND快閃記憶體累積需求就將達到Petabyte,這凸顯了閃存在彌合記憶體和冷資料儲存效能差距方面的重要作用。採購藍圖越來越重視30TB至100TB的企業級硬碟,三星將於2024年發表的128TB BM1743 SSD就反映了這一轉變。由此產生的拉動效應正在加速層級創新和控制器級壓縮技術的發展,從而保持NAND快閃記憶體市場的成長動能。

5G和大規模物聯網設備採用

獨立組網5G的引入將推動邊緣分析、智慧工廠、聯網汽車和智慧電網等應用場景的發展,使本地非揮發性儲存成為即時決策引擎的關鍵。西部數據的一份白皮書預測,隨著工業模組容量超過8GB,NOR快閃記憶體將向NAND快閃記憶體過渡。半導體藍圖目前優先考慮擴展溫度範圍的QLC晶粒和符合車規標準的NVMe設計,從而將NAND快閃記憶體市場擴展至運輸和基礎設施領域。

高密度電池的耐久極限

QLC 的 1000-3000 次程式設計/擦除循環次數閾值對於日誌密集型資料庫而言仍然不足,迫使用戶過度配置,從而抵消了其成本優勢。 Hackaday 指出,由於 300 層堆疊結構中電子陷阱的加速劣化,其物理極限正逐漸接近。雖然先進的糾錯和損耗均衡演算法可以緩解劣化,但 PLC 和 Crosspoint 等替代儲存技術仍在開發中,在它們的耐久性得到驗證之前,它們很可能仍會限制某些NAND快閃記憶體市場的發展。

細分市場分析

由於TLC閃存在耐用性和成本方面實現了卓越的平衡,其在NAND快閃記憶體快閃記憶體市場佔據了63.58%的佔有率。同時,QLC快閃記憶體正以6.35%的複合年成長率加速成長,超大規模資料中心業者中心在人工智慧資料湖領域展現出8-16倍的密度優勢,預計到2031年,QLC閃存在NAND快閃記憶體快閃記憶體市場的整體佔有率將進一步提升。三星的280層QLC原型展示了16TB單面M.2固態硬碟的發展藍圖,該硬碟既能滿足推理叢集的處理容量要求,又能減少機架面積。控制器級SLC快取技術和片上ECC技術縮小了與TLC快閃記憶體相比的延遲差距,從而促進了各種工作負載(例如視訊點播庫和備份儲存庫)的遷移。 TLC閃存在寫入密集型ERP和OLTP環境中依然保持優勢,其超過10,000次的循環壽命確保了可預測的服務品質。

在消費級筆記型電腦領域,TLC卓越的功耗特性將維持其市場佔有率,但QLC每位元成本的持續下降已對中階產品構成壓力。美光第六代QLC相比第一代產品,讀取延遲降低了34%,從而縮小了兩者之間的效能差距。隨著韌體定義的耐久性指標日趨成熟,OEM廠商將推出分級產品線,高容量產品採用QLC,而高階產品則繼續沿用先進的TLC製程。這種相互制約的趨勢將使兩種技術在預測期內繼續主導NAND快閃記憶體快閃記憶體市場。

從平面堆疊到垂直堆疊的過渡已接近完成,預計到2025年,3D NAND將佔據NAND快閃記憶體市場86.85%的佔有率。層數方面的技術突破,例如SK海力士的商用321層TLC和三星的400層V-NAND,顯示到本十年末,500層大關必將被突破。其經濟合理性顯而易見:垂直擴展可以在不縮小單元尺寸的情況下提高容量,從而規避光刻技術的限制。 2D NAND將繼續在航太和國防模組等細分領域佔有一席之地,在這些領域,超低寫入延遲比容量更為重要。

增加層數會加劇佈線電阻和單元間干擾。為了克服這個問題,鎧俠(Kioxia)的CMOS鍵結陣列策略隔離了外圍電路,從而提高了超堆疊結構的I/O效率和產量比率。三星正在探索用於奶油界面閘極的氧化鉿鐵電也旨在實現類似的目標:在堆疊高度增加時保持閾值電壓裕度。

NAND快閃記憶體報告依類型(SLC(單層單元)、MLC(多層單元)、TLC(三層單元)、QLC(四層單元))、結構(2D(平面)NAND、3D NAND)、介面(SATA、PCIe/NVMe、UFS/eMMC)、應用程式(智慧型手機、固態硬碟(PC、主機)主機、企業區和遊戲中心進行固態硬碟)。市場預測以美元計價。

區域分析

亞太地區在韓國垂直整合巨頭和中國龐大的設備組裝基地的支持下,預計到2025年將佔全球收入的55.40%。三星第九代V-NAND(286層)的量產以及SK海力士321層TLC生產線的推出,凸顯了該地區的技術優勢。總部位於北京的國內領導企業長江儲存(YMTC)不顧出口限制,正大力推動232層QLC製程的研發,這顯示其國內產能的擴張將使亞太地區繼續保持其在NAND快閃記憶體快閃記憶體市場的主導地位。

北美在營收方面保持第二的位置,這主要得益於雲端領域的資本投資需求。 《晶片與科學法案》為美光公司1,250億美元的國內巨型晶圓廠建設計畫資金籌措,預計到2035年,該計畫將提升美國在先進記憶體領域的自給自足能力。加拿大貢獻了控制器IP設計人才,而墨西哥則根據美墨加協定(USMCA)擴大了模組級組裝,從而增強了全部區域的供應鏈多元化。

由於儲存晶圓產能的限制,歐洲的市佔率仍維持在個位數中段。然而,德國和法國的汽車及工業OEM廠商對車規級NVMe模組的需求強勁。諸如歐洲綠色交易等永續性指令正在推動對節能型PCIe 5.0固態硬碟的需求,這類硬碟能夠降低機架能耗密度。歐洲晶圓廠正致力於利用新一代3D NAND製程(讀取消費量低於3pJ/bit)來搶佔這一市場。

中東和非洲地區以8.21%的複合年成長率呈現最高成長率。沙烏地阿拉伯的「2030願景」正在推動利雅德周邊晶圓後端一體化產業鏈的建設,而阿布達比政府投資機構則正尋求透過與一家控制器專家成立合資企業來建立區域供應鏈。豐富的可再生能源和極具吸引力的稅收政策正在吸引封裝合作夥伴,為在地化生產奠定基礎,從而推動海灣合作理事會(GCC)資料中心NAND快閃記憶體快閃記憶體市場的滲透。

其他福利:

- Excel格式的市場預測(ME)表

- 3個月的分析師支持

目錄

第1章 引言

- 研究假設和市場定義

- 調查範圍

第2章調查方法

第3章執行摘要

第4章 市場情勢

- 市場概覽

- 市場促進因素

- 資料中心對人工智慧/機器學習儲存的需求快速成長

- 5G和大規模物聯網設備採用

- PC/主機硬碟到固態硬碟的遷移

- 將業務策略轉向成本效益高的QLC固態硬碟

- 國內本土NAND製造計劃

- CXL 運算儲存採用情況

- 市場限制

- 高密度電池的耐久極限

- 價格週期性和資本投資負擔

- 由於出口限制,設備供不應求

- 高層工廠的永續性審查

- 產業供應鏈分析

- 監管環境

- 技術展望

- 宏觀經濟因素的影響

- 波特五力分析

- 供應商的議價能力

- 買方的議價能力

- 新進入者的威脅

- 替代品的威脅

- 競爭對手之間的競爭

第5章 市場規模與成長預測

- 按類型

- SLC(單層單元)

- MLC(多層細胞)

- TLC(三層板)

- QLC(四層池)

- 按結構

- 2D(平面)NAND

- 3D NAND

- 透過介面

- SATA

- PCIe/NVMe

- UFS/eMMC

- 透過使用

- 智慧型手機

- 固態硬碟(適用於PC和主機)

- 企業/資料中心固態硬碟

- 記憶卡和USB

- 工業和汽車電子

- 按地區

- 北美洲

- 美國

- 加拿大

- 墨西哥

- 南美洲

- 巴西

- 阿根廷

- 其他南美洲

- 歐洲

- 德國

- 英國

- 法國

- 義大利

- 西班牙

- 俄羅斯

- 其他歐洲地區

- 亞太地區

- 中國

- 日本

- 印度

- 韓國

- 東南亞

- 亞太其他地區

- 中東和非洲

- 中東

- 沙烏地阿拉伯

- 阿拉伯聯合大公國

- 土耳其

- 其他中東地區

- 非洲

- 南非

- 奈及利亞

- 其他非洲地區

- 中東

- 北美洲

第6章 競爭情勢

- 市場集中度

- 策略趨勢

- 市佔率分析

- 公司簡介

- Samsung Electronics Co., Ltd.

- SK hynix Inc.

- KIOXIA Holdings Corporation

- Western Digital Corporation

- Micron Technology, Inc.

- Nanya Technology Corporation

- Powerchip Technology Corporation

- Winbond Electronics Corporation

- Macronix International Co., Ltd.

- Silicon Motion Technology Corp.

- Phison Electronics Corp.

- Kingston Technology Company, Inc.

- ADATA Technology Co., Ltd.

- Transcend Information, Inc.

- GigaDevice Semiconductor Inc.

- SK Group(Solid-State Storage division)

- PNY Technologies, Inc.

- Team Group Inc.

- Longsys Electronics Co., Ltd.

- Smart Modular Technologies, Inc.

第7章 市場機會與未來展望

NAND flash memory market size in 2026 is estimated at USD 58.69 billion, growing from 2025 value of USD 55.73 billion with 2031 projections showing USD 76.03 billion, growing at 5.32% CAGR over 2026-2031.

This steady expansion is powered by hyperscale data-center capital spending on artificial-intelligence training clusters, the transition of client PCs and game consoles to solid-state storage, and vertically-scaled 3D architectures that keep cost-per-bit on a declining path. At the same time, national incentives to localize semiconductor fabrication, especially in the United States and Saudi Arabia, are strengthening regional supply resilience. Layer-count breakthroughs above 300 layers and PCIe 5.0 adoption are shortening replacement cycles for both enterprise and consumer SSDs. The confluence of 5G rollouts and massive IoT endpoints further widens addressable demand, positioning the NAND flash memory market for durable mid-single-digit growth horizons.

Global NAND Flash Memory Market Trends and Insights

Data-center AI/ML storage surge

Hyperscale operators are redesigning storage hierarchies so that NVMe SSD pools sit closer to GPU clusters, sustaining multi-gigabyte-per-second throughput for retrieval-augmented generation workloads. Western Digital estimates cumulative demand of 19,000 petabytes of NAND by 2029 for 5G-enabled endpoints alone, underscoring flash's role in bridging memory and cold-storage performance gaps. Procurement roadmaps increasingly favor 30 TB to 100 TB enterprise drives, a shift visible in Samsung's 128 TB BM1743 SSD showcased in 2024. The resulting pull-through effect accelerates layer-count innovation and controller-level compression techniques that sustain the NAND flash memory market momentum.

5G and massive-IoT device proliferation

Standalone 5G deployments unlock edge analytics use cases, smart factories, connected cars, and smart grids that mandate local non-volatile storage for real-time decision engines. Western Digital's white paper anticipates a NOR-to-NAND crossover within industrial modules as capacities climb above 8 GB. Semiconductor roadmaps now prioritize extended-temperature QLC die and automotive-qualified NVMe designs, broadening the NAND flash memory market footprint across transportation and infrastructure domains.

Endurance limits of high-density cells

QLC's 1,000-3,000 program/erase thresholds remain insufficient for log-heavy databases, forcing over-provisioning that erodes cost benefits. Hackaday notes the physics ceiling approaching as electron-trap wear accelerates in 300-layer stacks. Although advanced error-correction and wear-leveling algorithms offset degradation, alternate memories such as PLC or cross-point remain on the horizon, tempering portions of the NAND flash memory market until longevity is proven.

Other drivers and restraints analyzed in the detailed report include:

- PC/Console transition from HDD to SSD

- Enterprise pivot to cost-efficient QLC SSDs

- Pricing cyclicality and cap-ex burden

For complete list of drivers and restraints, kindly check the Table Of Contents.

Segment Analysis

The NAND flash memory market size for TLC devices held a 63.58% market share with the strength of balanced endurance and cost. QLC, however, is accelerating at 6.35% CAGR as hyperscalers validate its 8-16X density advantage for AI data-lakes, which lifts the overall NAND flash memory market share allocated to QLC by 2031. Samsung's 280-layer QLC prototype signals a roadmap to 16 TB single-sided M.2 drives, shrinking rack footprints while meeting throughput rules for inference clusters. Controller-level SLC-cache techniques and on-die ECC are narrowing the latency gap with TLC, encouraging broader workloads such as VOD libraries and backup repositories to migrate. TLC will retain primacy in write-intensive ERP and OLTP environments where its 10,000-plus cycle rating secures predictable quality-of-service.

In consumer notebooks, TLC's favorable power profile sustains its install base, but falling QLC cost-per-bit is already pressuring mid-range SKUs. Micron's sixth-gen QLC exhibits 34% lower read latency than first-gen samples, eroding the perceived performance divide. As firmware-defined endurance mitigation matures, OEMs will likely introduce tiered offerings where high-capacity SKUs employ QLC, while premium lines continue on advanced TLC nodes. This interplay keeps both technologies central to the NAND flash memory market over the forecast horizon.

The shift from planar to vertical stacking is virtually complete: 3D NAND commanded 86.85% of the NAND flash memory market share in 2025. Layer-count breakthroughs, SK Hynix's commercial 321-layer TLC and Samsung's 400-plus-layer V-NAND, signal confident scaling beyond the 500-layer watermark before decade-end. The economic logic is clear; vertical scaling adds capacity without shrinking cell size, sidestepping lithography constraints. 2D NAND survives in niche aerospace and defense modules where ultra-low-latency writes outweigh capacity.

Layer additions do stress interconnect resistance and cell-to-cell interference. To overcome this, Kioxia's CMOS-bonded-array strategy decouples peripheral circuits, boosting I/O efficiency and improving yield in ultra-tall stacks. Samsung's exploration of hafnia ferroelectrics for creamy-interface gates pursues a similar aim: maintain threshold-voltage margins even as stack height extends.

The NAND Flash Memory Report is Segmented by Type (SLC (Single-Level Cell), MLC (Multi-Level Cell), TLC (Triple-Level Cell), and QLC (Quad-Level Cell)), Structure (2D (Planar) NAND, and 3D NAND), Interface (SATA, Pcie / NVMe, and UFS / EMMC), Application (Smartphones, Solid-State Drives (PC and Console), Enterprise / Data-Center SSD, and More), and Geography. The Market Forecasts are Provided in Terms of Value (USD).

Geography Analysis

Asia-Pacific contributed 55.40% of sales in 2025, anchored by South Korea's vertically-integrated champions and China's colossal device assembly base. Samsung's mass production of 9th-generation V-NAND (286 layers) and SK Hynix's 321-layer TLC line affirm the region's technology lead. Beijing's domestic champion YMTC pushes 232-layer QLC nodes despite export-control constraints, illustrating indigenous capacity expansion that preserves Asia-Pacific's outsized influence on the NAND flash memory market.

North America sits second on revenue league tables, propelled by cloud capital-expenditure intensity. The CHIPS and Science Act bankrolls Micron's USD 125 billion state-side megafab roadmap, lifting U.S. advanced-memory self-sufficiency by 2035. Canada contributes controller-IP design talent, while Mexico scales module-level assembly lines under USMCA provisions, together reinforcing regional supply diversification.

Europe registers mid-single-digit share, constrained by limited memory wafer fabrication. Nonetheless, automotive and industrial OEMs in Germany and France generate robust demand for auto-grade NVMe modules. Sustainability directives such as the European Green Deal pivot buyers toward power-efficient PCIe 5.0 SSDs that lower rack energy density, a niche European fabs aim to capture through next-generation 3D NAND nodes with under-3 pJ/bit read energy footprints.

The Middle East and Africa present the highest growth rate at 8.21% CAGR. Saudi Arabia's Vision 2030 underwrites wafer-to-back-end complexes around Riyadh, while Abu Dhabi's sovereign investors explore joint-ventures with controller specialists to bootstrap a regional supply chain. Ample renewable-energy pipelines and attractive tax regimes draw packaging partners, setting the stage for localized production that boosts the NAND flash memory market penetration across GCC data hubs.

- Samsung Electronics Co., Ltd.

- SK hynix Inc.

- KIOXIA Holdings Corporation

- Western Digital Corporation

- Micron Technology, Inc.

- Nanya Technology Corporation

- Powerchip Technology Corporation

- Winbond Electronics Corporation

- Macronix International Co., Ltd.

- Silicon Motion Technology Corp.

- Phison Electronics Corp.

- Kingston Technology Company, Inc.

- ADATA Technology Co., Ltd.

- Transcend Information, Inc.

- GigaDevice Semiconductor Inc.

- SK Group (Solid-State Storage division)

- PNY Technologies, Inc.

- Team Group Inc.

- Longsys Electronics Co., Ltd.

- Smart Modular Technologies, Inc.

Additional Benefits:

- The market estimate (ME) sheet in Excel format

- 3 months of analyst support

TABLE OF CONTENTS

1 INTRODUCTION

- 1.1 Study Assumptions and Market Definition

- 1.2 Scope of the Study

2 RESEARCH METHODOLOGY

3 EXECUTIVE SUMMARY

4 MARKET LANDSCAPE

- 4.1 Market Overview

- 4.2 Market Drivers

- 4.2.1 Data-center AI/ML storage surge

- 4.2.2 5G and massive-IoT device proliferation

- 4.2.3 PC/Console transition from HDD to SSD

- 4.2.4 Enterprise pivot to cost-efficient QLC SSDs

- 4.2.5 National on-shore NAND fab programs

- 4.2.6 CXL-enabled computational storage adoption

- 4.3 Market Restraints

- 4.3.1 Endurance limits of high-density cells

- 4.3.2 Pricing cyclicality and cap-ex burden

- 4.3.3 Export-control induced equipment bottlenecks

- 4.3.4 Sustainability scrutiny on high-layer fabs

- 4.4 Industry Supply Chain Analysis

- 4.5 Regulatory Landscape

- 4.6 Technological Outlook

- 4.7 Impact of Macroeconomic Factors

- 4.8 Porter's Five Forces Analysis

- 4.8.1 Bargaining Power of Suppliers

- 4.8.2 Bargaining Power of Buyers

- 4.8.3 Threat of New Entrants

- 4.8.4 Threat of Substitutes

- 4.8.5 Intensity of Competitive Rivalry

5 MARKET SIZE AND GROWTH FORECASTS (VALUE)

- 5.1 By Type

- 5.1.1 SLC (Single-Level Cell)

- 5.1.2 MLC (Multi-Level Cell)

- 5.1.3 TLC (Triple-Level Cell)

- 5.1.4 QLC (Quad-Level Cell)

- 5.2 By Structure

- 5.2.1 2D (Planar) NAND

- 5.2.2 3D NAND

- 5.3 By Interface

- 5.3.1 SATA

- 5.3.2 PCIe / NVMe

- 5.3.3 UFS / eMMC

- 5.4 By Application

- 5.4.1 Smartphones

- 5.4.2 Solid-State Drives (PC and Console)

- 5.4.3 Enterprise / Data-center SSD

- 5.4.4 Memory Cards and USB Drives

- 5.4.5 Industrial and Automotive Electronics

- 5.5 By Geography

- 5.5.1 North America

- 5.5.1.1 United States

- 5.5.1.2 Canada

- 5.5.1.3 Mexico

- 5.5.2 South America

- 5.5.2.1 Brazil

- 5.5.2.2 Argentina

- 5.5.2.3 Rest of South America

- 5.5.3 Europe

- 5.5.3.1 Germany

- 5.5.3.2 United Kingdom

- 5.5.3.3 France

- 5.5.3.4 Italy

- 5.5.3.5 Spain

- 5.5.3.6 Russia

- 5.5.3.7 Rest of Europe

- 5.5.4 Asia-Pacific

- 5.5.4.1 China

- 5.5.4.2 Japan

- 5.5.4.3 India

- 5.5.4.4 South Korea

- 5.5.4.5 South-East Asia

- 5.5.4.6 Rest of Asia-Pacific

- 5.5.5 Middle East and Africa

- 5.5.5.1 Middle East

- 5.5.5.1.1 Saudi Arabia

- 5.5.5.1.2 United Arab Emirates

- 5.5.5.1.3 Turkey

- 5.5.5.1.4 Rest of Middle East

- 5.5.5.2 Africa

- 5.5.5.2.1 South Africa

- 5.5.5.2.2 Nigeria

- 5.5.5.2.3 Rest of Africa

- 5.5.5.1 Middle East

- 5.5.1 North America

6 COMPETITIVE LANDSCAPE

- 6.1 Market Concentration

- 6.2 Strategic Moves

- 6.3 Market Share Analysis

- 6.4 Company Profiles (includes Global level Overview, Market level overview, Core Segments, Financials as available, Strategic Information, Market Rank/Share for key companies, Products and Services, and Recent Developments)

- 6.4.1 Samsung Electronics Co., Ltd.

- 6.4.2 SK hynix Inc.

- 6.4.3 KIOXIA Holdings Corporation

- 6.4.4 Western Digital Corporation

- 6.4.5 Micron Technology, Inc.

- 6.4.6 Nanya Technology Corporation

- 6.4.7 Powerchip Technology Corporation

- 6.4.8 Winbond Electronics Corporation

- 6.4.9 Macronix International Co., Ltd.

- 6.4.10 Silicon Motion Technology Corp.

- 6.4.11 Phison Electronics Corp.

- 6.4.12 Kingston Technology Company, Inc.

- 6.4.13 ADATA Technology Co., Ltd.

- 6.4.14 Transcend Information, Inc.

- 6.4.15 GigaDevice Semiconductor Inc.

- 6.4.16 SK Group (Solid-State Storage division)

- 6.4.17 PNY Technologies, Inc.

- 6.4.18 Team Group Inc.

- 6.4.19 Longsys Electronics Co., Ltd.

- 6.4.20 Smart Modular Technologies, Inc.

7 MARKET OPPORTUNITIES AND FUTURE OUTLOOK

- 7.1 White-space and Unmet-Need Assessment