|

市場調查報告書

商品編碼

1982267

晶圓級封裝市場機會、成長要素、產業趨勢分析及2026-2035年預測。Wafer Level Packaging Market Opportunity, Growth Drivers, Industry Trend Analysis, and Forecast 2026 - 2035 |

||||||

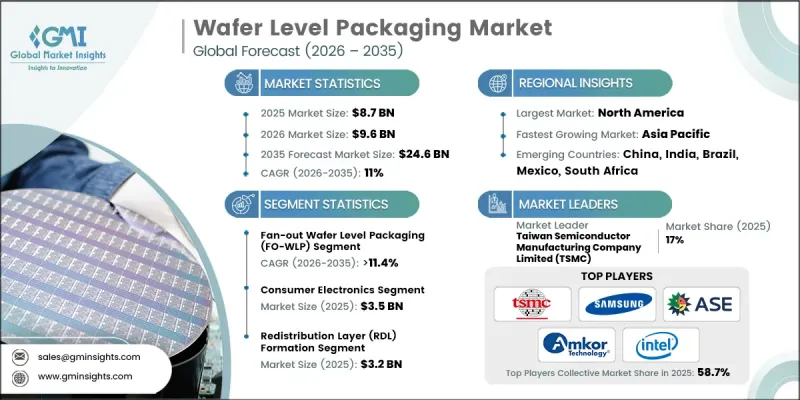

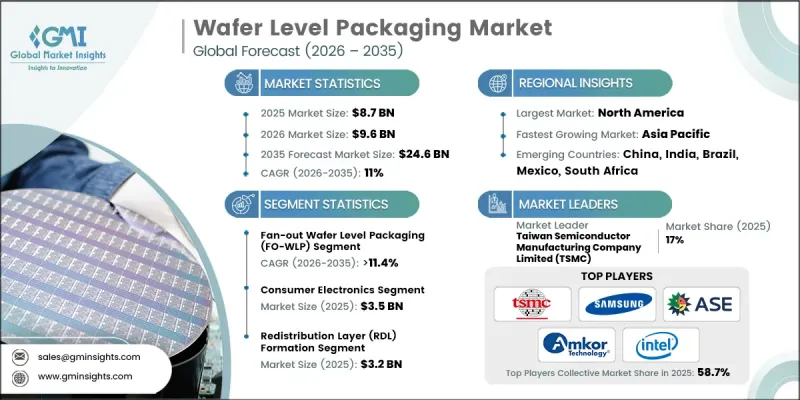

2025年全球晶圓層次電子構裝市場價值為87億美元,預計2035年將以11%的複合年成長率成長至246億美元。

晶圓層次電子構裝是一種先進的半導體製造技術,它在晶圓階段完成封裝,即在晶片分離之前。這種方法支援緊湊的尺寸、高效的散熱和多晶片整合,從而提升先進電子系統的性能。隨著業界對更高運算能力、能源效率和小型化的需求不斷成長,晶圓層次電子構裝正成為支撐下一代半導體創新的關鍵要素。該技術透過簡化生產流程,提高了互連密度,改善了訊號完整性,並帶來了成本優勢。數據驅動型、汽車和連網生態系統對高效能、高整合半導體元件的需求日益成長,正在加速晶圓級封裝的普及應用。製造商正在優先考慮可擴展的封裝架構,以適應不斷演變的複雜設計,同時保持產量比率最佳化和可靠性標準。總而言之,晶圓級封裝在全球半導體價值鏈中正日益佔據戰略重要地位。

| 市場範圍 | |

|---|---|

| 開始年份 | 2025 |

| 預測期 | 2026-2035 |

| 上市時的市場規模 | 87億美元 |

| 預測金額 | 246億美元 |

| 複合年成長率 | 11% |

在各個行業中,先進半導體節點的採用率正在迅速提高,以提升裝置性能和整合密度。晶圓層次電子構裝實現了晶圓級堆疊和先進的互連解決方案,從而支援為新興連接平台、電動出行系統和資料密集型基礎設施開發高可靠性半導體產品。現代半導體應用需要精確的溫度控管、更高的產量比率和高密度互連架構,以滿足複雜整合的需求。晶圓層次電子構裝技術支援扇出結構和麵板級擴充性,為用於先進運算和智慧型系統的3D積體電路和感測器模組提供穩健的堆疊解決方案。晶片組架構、先進的重線路重布、光電相容性以及人工智慧驅動的組裝製程的整合進一步提高了封裝效率。

扇出型晶圓級封裝 (FOWLP) 市場預計在 2025 年達到 36 億美元,並在 2026 年至 2035 年間以 11.4% 的複合年成長率成長。由於其能夠實現更高的輸入/輸出密度、更短的走線長度以及更優異的電氣和熱性能,該細分市場佔據了晶圓層次電子構裝市場最大的佔有率。其設計適應性和與異質整合架構的兼容性鞏固了其在先進半導體製造領域的地位。為了滿足不斷成長的需求,製造商正致力於開發耐用、高性能的扇出型解決方案,並輔以先進的重線路重布、創新的封裝材料和可擴展的面板級加工工具。

預計2025年,線路重布形成領域的市場規模將達32億美元,主要驅動力是技術進步。該領域的擴張得益於晶片級設計和3D異構整合在複雜度高的半導體應用中的日益普及。線路重布技術能夠實現邏輯、記憶體和電源組件之間的高密度互連,從而支援先進的半導體功能並增強系統整合。

預計到2025年,北美晶圓層次電子構裝市佔率將達到42.6%。該地區的成長主要得益於強勁的半導體研發活動、旨在提升國內製造能力的聯邦資助舉措,以及對高效能處理器和先進運算平台日益成長的需求。封裝創新和在先進半導體製造領域的領先地位,持續鞏固北美在全球市場的主導地位。

目錄

第1章:調查方法和範圍

第2章執行摘要

第3章業界考察

- 生態系分析

- 供應商情況

- 利潤率

- 成本結構

- 每個階段增加的價值

- 影響價值鏈的因素

- 中斷

- 影響產業的因素

- 促進因素

- 行動和穿戴式裝置對小型化的需求日益成長

- 人工智慧加速器和高頻寬記憶體的成長

- 汽車電子和ADAS的擴展

- 5G和邊緣運算設備的普及

- 人們越來越關注大規模生產中的成本降低問題。

- 產業潛在風險與挑戰

- 面板級WLP小型化帶來的高昂設備成本

- 超薄晶圓產量比率的技術挑戰

- 市場機遇

- 採用晶片組架構和先進的SiP技術

- 軟性/混合電子和光電的發展

- 促進因素

- 成長潛力分析

- 監理情勢

- 北美洲

- 歐洲

- 亞太地區

- 拉丁美洲

- 中東和非洲

- 波特五力分析

- PESTEL 分析

- 科技與創新趨勢

- 當前技術趨勢

- 新興技術

- 新興經營模式

- 合規要求

- 專利分析

第4章 競爭情勢

- 介紹

- 企業市佔率分析

- 按地區

- 北美洲

- 歐洲

- 亞太地區

- 拉丁美洲

- 中東和非洲

- 市場集中度分析

- 按地區

- 主要企業的競爭標竿分析

- 財務績效比較

- 銷售量

- 利潤率

- 研究與開發

- 產品系列比較

- 產品線

- 科技

- 創新

- 區域擴張比較

- 全球擴張分析

- 服務網路覆蓋

- 按地區分類的市場滲透率

- 競爭定位矩陣

- 領導者

- 挑戰者

- 追蹤者

- 小眾玩家

- 戰略展望矩陣

- 財務績效比較

- 2022-2025 年重大發展

- 併購

- 夥伴關係和聯盟

- 技術進步

- 業務拓展與投資策略

- 永續發展計劃

- 數位轉型計劃

- 新興/Start-Ups競爭對手的發展趨勢

第5章 市場估價與預測:依包裝技術分類,2022-2035年

- ,

- 晶圓級晶片封裝(WLCSP/WL-CSP)

- 扇入式晶圓級封裝(FI-WLP)

- 扇出型晶圓級封裝(FO-WLP)

第6章 市場估價與預測:依製程分類,2022-2035年

- 線路重布(RDL)形成

- 晶圓凸塊

- 晶圓級凸塊下金屬化(UBM)

- 晶圓級鈍化和保護層

- 晶圓減薄和背面研磨

第7章 市場估計與預測:依材料分類,2022-2035年

- RDL材料

- 介電和鈍化材料

- 焊料和銅線材料

- 晶圓級封裝化合物

第8章 市場估算與預測:依最終用途分類,2022-2035年

- 家用電子電器

- 汽車電子

- 工業電子設備

- 物聯網設備

- 通訊設備

- 其他

第9章 晶圓級封裝市場估價與預測:按地區分類,2022-2035年

- 按地區

- 北美洲

- 美國

- 加拿大

- 歐洲

- 英國

- 德國

- 法國

- 義大利

- 西班牙

- 荷蘭

- 其他歐洲地區

- 亞太地區

- 中國

- 印度

- 日本

- 韓國

- 澳洲

- 亞太其他地區

- 拉丁美洲

- 巴西

- 墨西哥

- 阿根廷

- 其他拉丁美洲地區

- 中東和非洲(MEA)

- 沙烏地阿拉伯

- 南非

- 阿拉伯聯合大公國

- 其他中東和非洲地區

第10章:公司簡介

- Amkor Technology, Inc.

- ASE Technology Holding Co., Ltd.

- China Wafer Level CSP Co., Ltd.

- ChipMOS Technologies Inc.

- Deca Technologies Inc.

- Fujitsu Limited

- HANA Micron Inc.

- Huatian Technology Co., Ltd.

- Intel Corporation

- Jiangsu Changjiang Electronics Technology Co., Ltd.(JCET Group)

- Powertech Technology Inc.(PTI)

- Samsung Electronics Co., Ltd.

- STATS ChipPAC Pte. Ltd.

- Taiwan Semiconductor Manufacturing Company Limited(TSMC)

- Tongfu Microelectronics Co., Ltd.

The Global Wafer Level Packaging Market was valued at USD 8.7 billion in 2025 and is estimated to grow at a CAGR of 11% to reach USD 24.6 billion by 2035.

Wafer level packaging is an advanced semiconductor manufacturing technique that completes the packaging process at the wafer stage before individual chip separation. This approach supports compact form factors, efficient thermal dissipation, and multi-die integration, enabling higher performance across advanced electronic systems. As industries push for greater computing capability, energy efficiency, and miniaturization, wafer level packaging is becoming a critical enabler of next-generation semiconductor innovation. The technology enhances interconnect density, improves signal integrity, and delivers cost advantages through streamlined production. Growing demand for high-performance and highly integrated semiconductor devices across data-driven, automotive, and connected ecosystems is accelerating adoption. Manufacturers are prioritizing scalable packaging architectures that address evolving design complexity while maintaining yield optimization and reliability standards. Overall, wafer level packaging continues to gain strategic importance within the global semiconductor value chain.

| Market Scope | |

|---|---|

| Start Year | 2025 |

| Forecast Year | 2026-2035 |

| Start Value | $8.7 Billion |

| Forecast Value | $24.6 Billion |

| CAGR | 11% |

Industries are rapidly adopting advanced semiconductor nodes to increase device performance and integration density. Wafer level packaging enables wafer-scale stacking and advanced interconnect solutions, supporting the development of high-reliability semiconductor products for emerging connectivity platforms, electrified mobility systems, and data-intensive infrastructure. Modern semiconductor applications require precise thermal management, enhanced yield performance, and dense interconnect architectures to meet complex integration demands. Wafer level packaging technologies support fan-out structures and panel-level scalability, enabling robust stacking solutions for three-dimensional integrated circuits and sensor modules used in advanced computing and intelligent systems. The integration of chiplet architectures, sophisticated redistribution layers, photonics compatibility, and AI-assisted assembly processes is further enhancing packaging efficiency.

The fan-out wafer level packaging segment was valued at USD 3.6 billion in 2025 and is estimated to grow at a CAGR of 11.4% during 2026-2035. This segment holds the largest share of the wafer level packaging market due to its ability to deliver higher input/output density, reduced interconnect length, and improved electrical and thermal performance. Its design adaptability and compatibility with heterogeneous integration architectures have strengthened its position in advanced semiconductor manufacturing. To address rising demand, manufacturers are focusing on durable, high-performance fan-out solutions supported by advanced redistribution layers, innovative molding materials, and scalable panel-level processing tools.

The redistribution layer formation segment generated USD 3.2 billion in 2025, leading the market by technology. This segment is expanding due to the increasing adoption of chiplet-based designs and three-dimensional heterogeneous integration in high-complexity semiconductor applications. Redistribution layer technology enables high-density interconnections between logic, memory, and power components, supporting advanced semiconductor functionality and enhanced system integration.

North America Wafer Level Packaging Market accounted for 42.6% share in 2025. Regional growth is driven by substantial semiconductor research and development activity, federal funding initiatives aimed at strengthening domestic fabrication capacity, and increasing demand for high-performance processors and advanced computing platforms. Leadership in packaging innovation and advanced semiconductor manufacturing continues to reinforce North America's dominant position within the global market.

Major companies operating in the Global Wafer Level Packaging Market include Taiwan Semiconductor Manufacturing Company Limited, Intel Corporation, Samsung Electronics Co., Ltd., ASE Technology Holding Co., Ltd., Amkor Technology, Inc., Jiangsu Changjiang Electronics Technology Co., Ltd., Powertech Technology Inc., Tongfu Microelectronics Co., Ltd., Huatian Technology Co., Ltd., ChipMOS Technologies Inc., China Wafer Level CSP Co., Ltd., HANA Micron Inc., STATS ChipPAC Pte. Ltd., Fujitsu Limited, and Deca Technologies Inc.. Companies competing in the Global Wafer Level Packaging Market are strengthening their competitive position through sustained investment in advanced packaging research and process innovation. Leading players are expanding panel-level manufacturing capabilities and developing next-generation redistribution layer technologies to improve integration density and thermal performance. Strategic collaborations with semiconductor foundries and system designers are enabling co-development of customized packaging architectures. Firms are also investing in automation, AI-driven inspection systems, and yield optimization tools to enhance production efficiency. Geographic expansion into emerging semiconductor hubs and capacity upgrades in advanced packaging facilities are supporting long-term growth.

Table of Contents

Chapter 1 Methodology and Scope

- 1.1 Market scope and definition

- 1.2 Research design

- 1.2.1 Research approach

- 1.2.2 Data collection methods

- 1.3 Data mining sources

- 1.3.1 Global

- 1.3.2 Regional/Country

- 1.4 Base estimates and calculations

- 1.4.1 Base year calculation

- 1.4.2 Key trends for market estimation

- 1.5 Primary research and validation

- 1.5.1 Primary sources

- 1.6 Forecast model

- 1.7 Research assumptions and limitations

Chapter 2 Executive Summary

- 2.1 Industry snapshot

- 2.2 Key market trends

- 2.2.1 Packaging type trends

- 2.2.2 Process trends

- 2.2.3 Material trends

- 2.2.4 End-use application trends

- 2.2.5 Regional trends

- 2.3 TAM Analysis, 2026-2035 (USD Billion)

- 2.4 CXO perspectives: Strategic imperatives

Chapter 3 Industry Insights

- 3.1 Industry ecosystem analysis

- 3.1.1 Supplier Landscape

- 3.1.2 Profit Margin

- 3.1.3 Cost structure

- 3.1.4 Value addition at each stage

- 3.1.5 Factor affecting the value chain

- 3.1.6 Disruptions

- 3.2 Industry impact forces

- 3.2.1 Growth drivers

- 3.2.1.1 Rising demand for miniaturization in mobile and wearables

- 3.2.1.2 Growth in AI accelerators and high-bandwidth memory

- 3.2.1.3 Expansion of automotive electronics and ADAS

- 3.2.1.4 Proliferation of 5G and edge computing devices

- 3.2.1.5 Increasing focus on cost reduction in high-volume production

- 3.2.2 Industry pitfalls and challenges

- 3.2.2.1 High equipment costs for panel-level WLP scaling

- 3.2.2.2 Technical challenges in yield for ultra-thin wafers

- 3.2.3 Market opportunities

- 3.2.3.1 Adoption of chiplet architectures and advanced SiPs

- 3.2.3.2 Growth in flexible/hybrid electronics and photonics

- 3.2.1 Growth drivers

- 3.3 Growth potential analysis

- 3.4 Regulatory landscape

- 3.4.1 North America

- 3.4.2 Europe

- 3.4.3 Asia Pacific

- 3.4.4 Latin America

- 3.4.5 Middle East & Africa

- 3.5 Porter's analysis

- 3.6 PESTEL analysis

- 3.7 Technology and innovation landscape

- 3.7.1 Current technological trends

- 3.7.2 Emerging technologies

- 3.8 Emerging business models

- 3.9 Compliance requirements

- 3.10 Patent analysis

Chapter 4 Competitive Landscape, 2025

- 4.1 Introduction

- 4.2 Company market share analysis

- 4.2.1 By Region

- 4.2.1.1 North America

- 4.2.1.2 Europe

- 4.2.1.3 Asia Pacific

- 4.2.1.4 Latin America

- 4.2.1.5 Middle East & Africa

- 4.2.2 Market Concentration Analysis

- 4.2.1 By Region

- 4.3 Competitive benchmarking of key players

- 4.3.1 Financial performance comparison

- 4.3.1.1 Revenue

- 4.3.1.2 Profit margin

- 4.3.1.3 R&D

- 4.3.2 Product portfolio comparison

- 4.3.2.1 Product range breadth

- 4.3.2.2 Technology

- 4.3.2.3 Innovation

- 4.3.3 Geographic presence comparison

- 4.3.3.1 Global footprint analysis

- 4.3.3.2 Service network coverage

- 4.3.3.3 Market penetration by region

- 4.3.4 Competitive positioning matrix

- 4.3.4.1 Leaders

- 4.3.4.2 Challengers

- 4.3.4.3 Followers

- 4.3.4.4 Niche players

- 4.3.5 Strategic outlook matrix

- 4.3.1 Financial performance comparison

- 4.4 Key developments, 2022-2025

- 4.4.1 Mergers and acquisitions

- 4.4.2 Partnerships and collaborations

- 4.4.3 Technological advancements

- 4.4.4 Expansion and investment strategies

- 4.4.5 Sustainability initiatives

- 4.4.6 Digital transformation initiatives

- 4.5 Emerging/ startup competitors landscape

Chapter 5 Market Estimates & Forecast, By Packaging Technology, 2022 - 2035 (USD Million)

- 5.1 Key trends,

- 5.2 Wafer-Level Chip Scale Packaging (WLCSP / WL-CSP)

- 5.3 Fan-In Wafer Level Packaging (FI-WLP)

- 5.4 Fan-Out Wafer Level Packaging (FO-WLP)

Chapter 6 Market Estimates and Forecast, By Process, 2022 - 2035 (USD Million)

- 6.1 Key trends

- 6.2 Redistribution Layer (RDL) formation

- 6.3 Wafer bumping

- 6.4 Wafer-level under-bump metallization (UBM)

- 6.5 Wafer-level passivation and protection layers

- 6.6 Wafer thinning and back grinding

Chapter 7 Market Estimates and Forecast, By Materials, 2022 - 2035 (USD Million)

- 7.1 Key trends

- 7.2 RDL materials

- 7.3 Dielectric and passivation materials

- 7.4 Solder and copper interconnect materials

- 7.5 Wafer-level encapsulation compounds

Chapter 8 Market Estimates and Forecast, By End-use Application, 2022 - 2035 (USD Million)

- 8.1 Key trends

- 8.2 Consumer electronics

- 8.3 Automotive electronics

- 8.4 Industrial electronics

- 8.5 IoT devices

- 8.6 Telecommunications devices

- 8.7 Others

Chapter 9 Wafer level packaging Market Estimates & Forecast, By Region, 2022 - 2035 (USD Million)

- 9.1 Key trends, by region

- 9.2 North America

- 9.2.1 U.S.

- 9.2.2 Canada

- 9.3 Europe

- 9.3.1 UK

- 9.3.2 Germany

- 9.3.3 France

- 9.3.4 Italy

- 9.3.5 Spain

- 9.3.6 Netherlands

- 9.3.7 Rest of Europe

- 9.4 Asia-Pacific

- 9.4.1 China

- 9.4.2 India

- 9.4.3 Japan

- 9.4.4 South Korea

- 9.4.5 Australia

- 9.4.6 Rest of Asia-Pacific

- 9.5 Latin America

- 9.5.1 Brazil

- 9.5.2 Mexico

- 9.5.3 Argentina

- 9.5.4 Rest of Latin America

- 9.6 MEA

- 9.6.1 Saudi Arabia

- 9.6.2 South Africa

- 9.6.3 UAE

- 9.6.4 Rest of MEA

Chapter 10 Company Profiles

- 10.1 Amkor Technology, Inc.

- 10.2 ASE Technology Holding Co., Ltd.

- 10.3 China Wafer Level CSP Co., Ltd.

- 10.4 ChipMOS Technologies Inc.

- 10.5 Deca Technologies Inc.

- 10.6 Fujitsu Limited

- 10.7 HANA Micron Inc.

- 10.8 Huatian Technology Co., Ltd.

- 10.9 Intel Corporation

- 10.10 Jiangsu Changjiang Electronics Technology Co., Ltd. (JCET Group)

- 10.11 Powertech Technology Inc. (PTI)

- 10.12 Samsung Electronics Co., Ltd.

- 10.13 STATS ChipPAC Pte. Ltd.

- 10.14 Taiwan Semiconductor Manufacturing Company Limited (TSMC)

- 10.15 Tongfu Microelectronics Co., Ltd.